FLOW-3Dによる はんだ付け のモデル化

工業化が進む現代社会において、電子部品は必要不可欠なものとなっています。

電子部品の製造における重要な技術の一つに はんだ付け が挙げられます。

はんだ付け は従来からある技術ですが、今日の環境問題からの要請(RoHS指令)で鉛フリーはんだが使用されるようになり、

以前は主流であった鉛はんだとは異なる特性を有しています。

さらに、製品開発からの要請などもあるため、従来の製造条件や方法などを変更する必要があります。

このような場合に、数値解析によるシミュレーションが役に立ちます。

電子部品と基板をはんだで接合する工業利用の方法として、

リフロー方式とフロー方式の2つに大別されます。ここでは、

これら2つの方式のはんだ付けに対するシミュレーション例を紹介します。

また、はんだ付けの特殊な問題例として、はんだ付けする接合領域を制御する問題が挙げられます。

このために有効な加工処理に関して、実験との比較を行ったシミュレーション事例も紹介します。

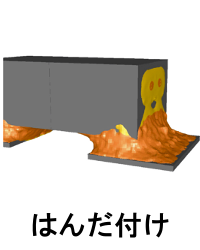

フロー方式

フロー方式のはんだ付けは、

はんだ槽にある溶融はんだの自由表面近傍に基板の下側の面を浸してはんだ付けを行う方法で、

主に比較的大きなサイズのはんだ付けに利用されています。

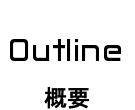

フロー方式で紹介する例の解析モデルを図1に示します。図1では、

はんだ槽上部から溶融はんだが湧き出しており、ここを基板が通過してはんだ付けされる工程の解析モデルを

表しています。溶融はんだは、基板の下面において、

- スルーホールへ流入し、

- はんだ槽を通過後に液切れするとともにスルーホールに付着し、

- 付着と同時に熱伝達で温度が低下して凝固していく、

という工程を経て電子部品と基板を接合します。

はんだがリード部で形成するフィレット形状や凝固収縮によって引き起こされる引け巣などの問題に着目して、

最適な製造条件を得るためにシミュレーションを利用できます。

図1 フロー方式の解析モデル

図2は、リード部中心断面での温度コンターを表しており、

溶融はんだがリードと接触してから液切れするまでの様子を時系列(左から右に向かう)に示しています。

![図2 フロー方式のはんだ付けの時系列[左→右] (リード部2D断面表示:温度コンター)](../wp-content/uploads/2014/02/fig21.png)

図2 フロー方式のはんだ付けの時系列[左→右]

(リード部2D断面表示:温度コンター)

リフロー方式

リフロー方式のはんだ付けは、プリント基板上にクリームはんだ(はんだペースト)を印刷して、

その上に電子部品を配置してから加熱・冷却制御してはんだ付けする方式で、

主に比較的小さいサイズのはんだ付けに利用されています。

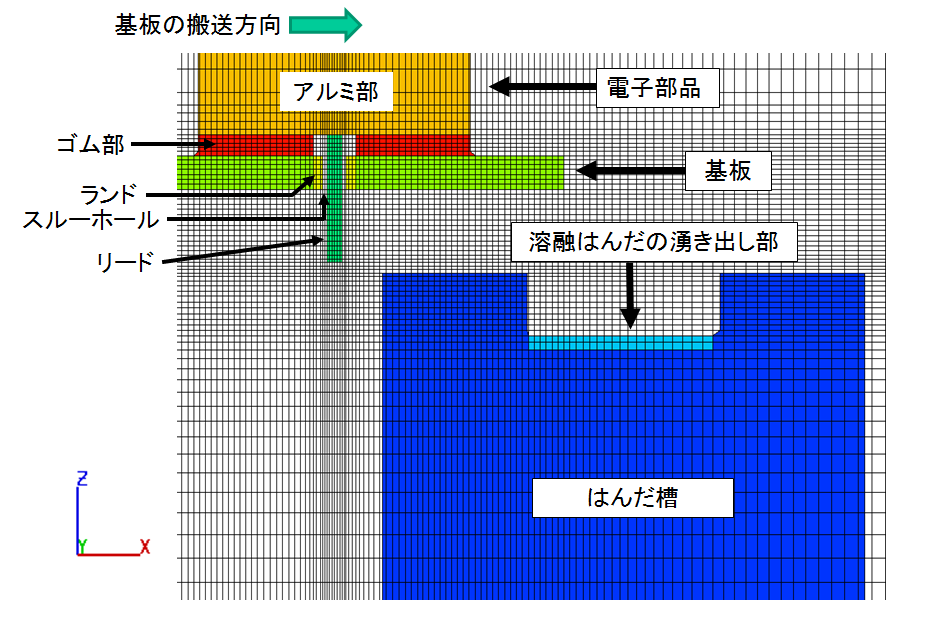

リフロー方式を用いた電子部品のはんだ付けにおける接合不良の代表的な例を図3に示します。

ここでは、図3の中から①と③の問題に対して実施した、はんだ接合シミュレーションの例を紹介します。シミュレーションにより、接合不良の発生要因を定量的に明らかにしていくことで、接合不良を低減あるいは撲滅していく改善方法を検討することができます。

図3 電子部品はんだ接合不良の代表例(資料提供:F社)

はんだブリッジ解析(資料提供:F社)

あらかじめ配置するはんだペースト量とリード間ピッチの関係が不適切な場合、

はんだブリッジや未はんだといった接合不良がおきます。

さらに、これらが適切な関係においても接合不良を生じる場合があります。

ここでは、その原因として表面状態の変化を仮定した場合の解析を実施します。

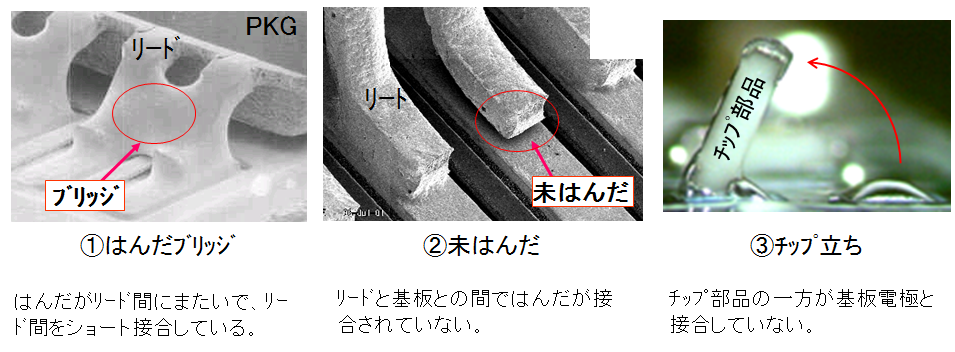

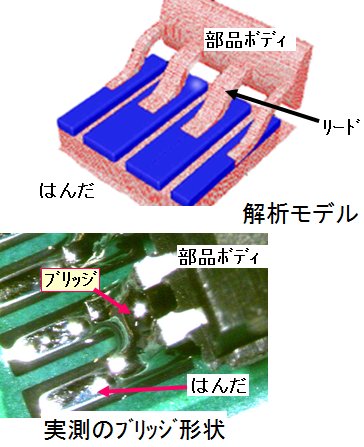

図4 解析対象の電子部品

はんだブリッジ解析の手順

- 図4の電子部品と基板をはんだで接合する

- はんだの加熱溶融から冷却凝固のプロセスを解析する

- はんだの濡れ広がり形状(2次元モデル)を

実測フィレット形状と比較検証する - はんだの濡れ広がり形状(3次元モデル)を

実測フィレット形状と比較検証する - はんだの接合不良(ブリッジ)を再現する

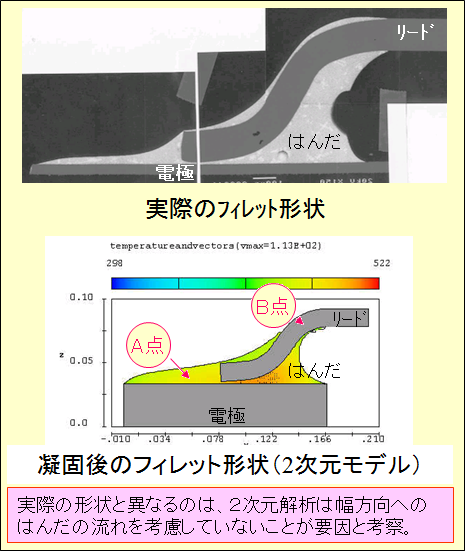

(1) 2次元モデルでの比較検証

実際の現象

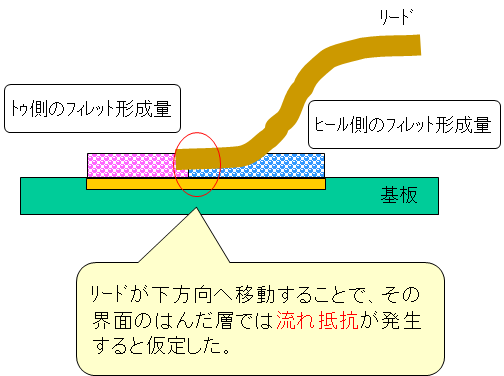

はんだ溶融時に、電子部品は重力による自重で基板方向に沈んでいくので、

これをあらかじめ計算条件で考慮しておきます。

図5 2次元モデル

図6 実測結果(上)と解析結果(下)

(2) 3次元モデルでの比較検証(1)

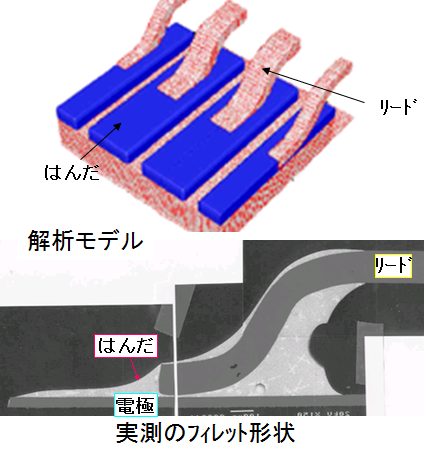

電子部品の対称性を考慮した部分領域の3次元モデルで解析し、

実際のはんだフィレット形状と比較検証する。最初は、正常な接合の場合を解析する。

図7 解析モデル(上)と実測結果(下)

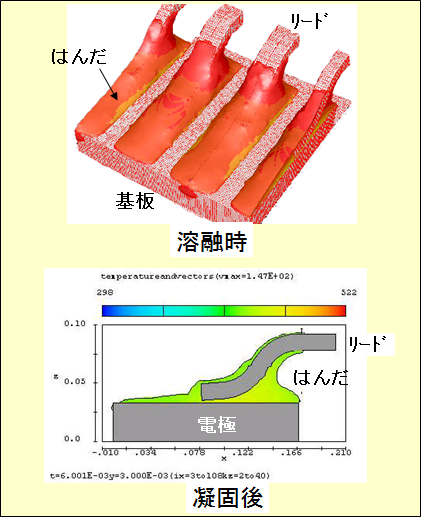

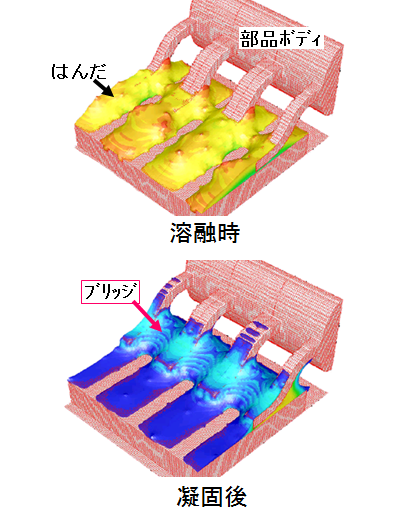

図8 解析結果:溶融時(上)と凝固後(下)

(3) 3次元モデルでの比較検証(2)

続いて、はんだブリッジが起こる場合を解析します。

ここでは、何らかの要因によりはんだが濡れ広がる領域の表面状態が変化したことを仮定して、解析を実施しました。

図9 解析モデル(上)と実測結果(下)

図10 溶融時(上)と凝固後(下)

チップ立ち

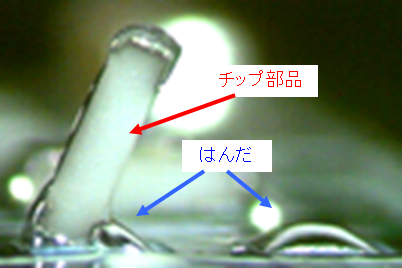

図11 チップ立ちの実測写真(凝固後)

リフロー方式において、電子部品をクリームはんだ上に初期配置するときに多少の位置ずれがあっても、はんだ溶融時に部品位置が自動的に正常な位置に修復される(セルフアラインメント効果)利点があります。

これは電子部品の微小化に伴い、はんだ溶融時に働く支配的な力として相対的に表面張力が卓越してくるために起こる効果で、部品に働く力のバランスの結果として見られる現象です。従って、はんだペースト量、はんだが接する材料との濡れ性、接触面積、はんだ溶融のタイミング(温度分布と時間変化)などが重要なファクタとなってきます。もし、部品に働く力がアンバランスとなる場合、図11に示すようなチップ立ちと呼ばれる接合不良を発生させることがあります。

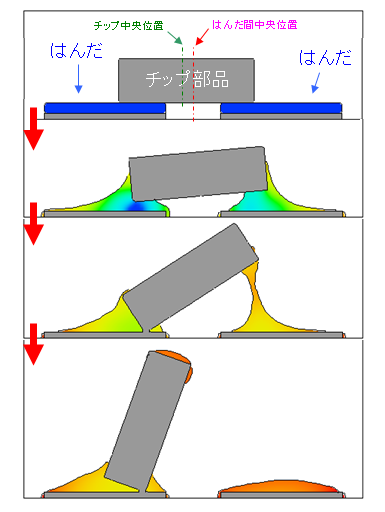

図12 チップ立ちの計算結果(時系列)

チップ部品に働く表面張力がアンバランスになる場合として、左右のはんだペースト量が異なる、

あるいは左右のはんだが溶融するタイミングが異なるなどの場合が考えられます。

また、高密度実装化が進められる基板では部品間距離が短くなるために、はんだペースト量を制限する必要があので、

セルフアラインメントによる修正可能な初期配置の位置ずれ許容範囲も狭くなってきます。

ここでは、セルフアラインメント効果の位置ずれ許容範囲が狭いケースにおいて、

チップの初期配置が要求された精度よりもずれた位置で配置された場合にチップ立ちを起こす例を紹介します。

はんだ付けの領域制御

図13 コイニング加工なし

図14 コイニング加工あり

詳細は、ユーザ事例(はんだ付けの領域制御 【資料提供:アルプス電気株式会社様】)をご覧ください。